Intel To Launch 3D XPoint DIMMs in 2H 2018

by Billy Tallis on November 14, 2017 6:20 PM EST

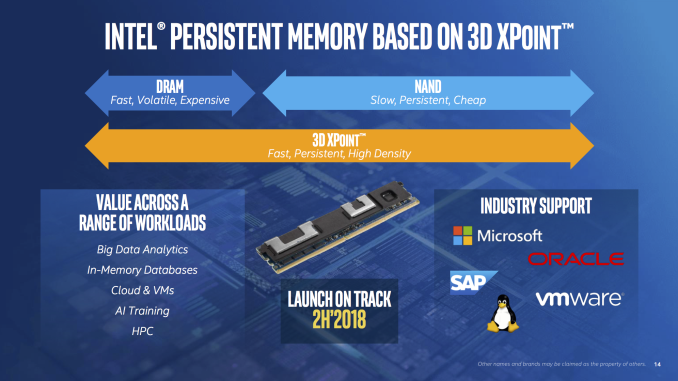

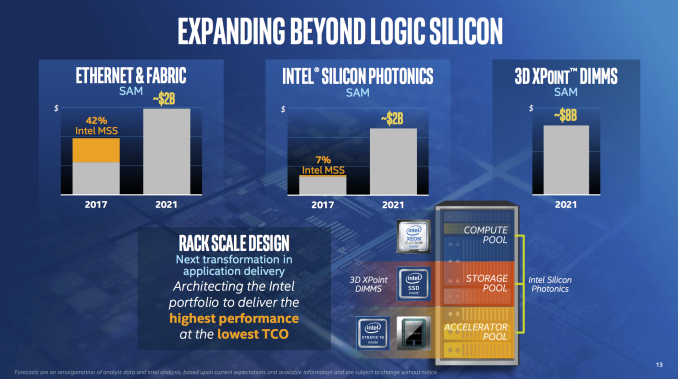

Presenting at the UBS Global Technology Conference today, Navin Shenoy, Intel Executive Vice President and General Manager of their Data Center Group, shared an update on Intel's roadmap for 3D XPoint DIMMs. Intel claims that they are on track to launch 3D XPoint memory modules in the second half of 2018. They are projecting that 3D XPoint DIMMs will be an $8B market by 2021.

After launching several Optane SSD products this year based on 3D XPoint memory, Intel had said almost nothing about their progress toward 3D XPoint DIMM memory modules. Intel first publicly showed a prototype 3D XPoint NVDIMM in January 2016, only a few months after unveiling 3D XPoint memory itself. When the first Optane products launched earlier this year, we were told Intel would have more to say on the subject of 3D XPoint DIMMs in 2018, but today's announcement makes it clear they will be selling the actual hardware within about a year.

The launch of 3D XPoint DIMMs will depend on several pieces coming together. First, Intel's 3D XPoint memory must be sufficiently mature to meet the performance and endurance requirements of DIMM-based usage. Their Optane SSDs have all used a PCIe and NVMe interface that adds substantial latency overhead and makes it difficult to assess how close the underlying 3D XPoint memory can come to DRAM performance levels. The Optane SSDs are also shipping with relatively conservative write endurance ratings relative to the eventual expectations for 3D XPoint products: The Optane SSD DC P4800X's 30 drive writes per day for 5 years is not significantly higher than high-endurance flash-based enterprise SSDs can provide.

Second, Intel will need to continue increasing production of 3D XPoint memory as their family of Optane SSDs expands and is joined by 3D XPoint DIMMs. Yesterday, Intel and Micron celebrated the completion of an expansion to building 60 of their IM Flash production facilities in Lehi, Utah. This will significantly increase their production capacity of 3D XPoint memory. So far, Intel seems to have been using almost all of the production of 3D XPoint memory for their Optane products while Micron has yet to publicly introduce any mass-produced 3D XPoint-based products. Micron will most likely start announcing and shipping 3D XPoint products under their QuantX brand within the next year, so Intel won't be getting the full benefit of this capacity boost.

Third, 3D XPoint DIMMs will require server platform support because they are unlikely to operate as standard DDR4 DIMMs. The JEDEC NVDIMM-P standard for persistent memory DIMMs has not been finalized and is expected next year. It's not certain whether the 3D XPoint DIMMs will adhere to the NVDIMM-P standard or if they will use a proprietary interface, but either way they are likely to require updated CPU and motherboard support. Intel's recently-launched Xeon Scalable platform can support DRAM+flash NVDIMM-N modules. The launch next year of 3D XPoint DIMMs may foretell a simultaneous refresh of the Xeon Scalable platform.

Source: Intel

58 Comments

View All Comments

inighthawki - Wednesday, November 15, 2017 - link

I know that interpreting sarcasm in text is sometimes difficult, but come on man, this one is really quite obvious.Elstar - Tuesday, November 14, 2017 - link

I love how Intel introduced and then deprecated one of the 3D XPoint, a.k.a. "persistent memory" instructions long before the product even started shipping:https://software.intel.com/en-us/blogs/2016/09/12/...

Zan Lynx - Wednesday, November 15, 2017 - link

You know they've been working toward this for many years now. They've patched the Linux kernel for NVDIMM, written ACPI rules, CPU instructions and many other things. If they discovered in testing that one of their instructions was a bad idea, it is good that they found out early.name99 - Wednesday, November 15, 2017 - link

Zan, I think that's a bad reading of the situation. To me the deprecation is more problematic.The deprecation forces the memory controller to be part of the power-fail-safe domain. Is the idea that future memory controllers will ALWAYS have enough capacitor capacity on the die/package/motherboard that they will be able to force out all pending writes when the system loses power? (And that means enough power not just to run the memory controller, but also to push out the writes meaning enough power to keep the nvDIMMs alive.)

What are the implication of this for non-server systems? In particular consider

(a) non-Intel (ie AMD) systems

(b) small systems (Surface sorts of things, or Atom and Quark type designs).

How onerous are these power storage requirements? Do they prevent the use of nvDIMMs in x86 small systems more or less forever (at least until a substantial technology reconfiguration)?

Hurr Durr - Wednesday, November 15, 2017 - link

Hyperam!ddriver - Wednesday, November 15, 2017 - link

Hype? Shut your blasphemous foul mouth! It will revolutionize everything!Samus - Wednesday, November 15, 2017 - link

I actually like the name HyperRam ;)ddriver - Wednesday, November 15, 2017 - link

That might have to do with your affinity for idiocy. Because it wouldn't be hyper in any way - performance will be total garbage compared to ram, and endurance will be like a couple of months at best if you use it as ram. Last but not least, because it not intended to be used as ram.But you go ahead and call it hyper ram, because like that other guy, the pinnacle of appreciation for you is liking mindless stuff :P

ironargonaut - Wednesday, November 15, 2017 - link

I know this is one of the most asked questions on Anandtech, but how do I block ddriver again? His drivel has finally passed my tolerance level.ddrіver - Wednesday, November 15, 2017 - link

Is this frustration because I am superior? I don't want to tickle my own balls but I could teach every single engineer at Intel some lessons.