AMD Discusses ‘X3D’ Die Stacking and Packaging for Future Products: Hybrid 2.5D and 3D

by Dr. Ian Cutress on March 5, 2020 5:00 PM EST- Posted in

- CPUs

- AMD

- GPUs

- HBM

- TSMC

- Packaging

- AMD FAD 2020

- X3D

- Die Stacking

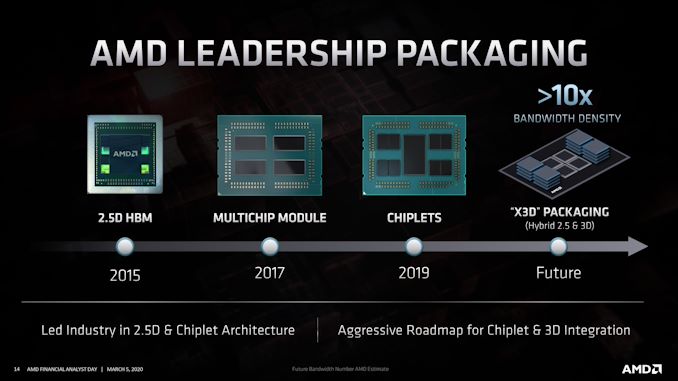

One of AMD’s key messages at its Financial Analyst Day 2020 is that the company wants to remain on the leading edge when it comes to process node technology as well as the latest packaging technology on its newest products. To that end, AMD discussed how it has surged forward with not only 2.5D interposer designs in its GPUs, but also stacked memory and chiplet implementations. The next stage of this journey, according to AMD, is a new X3D die stacking and packaging technology.

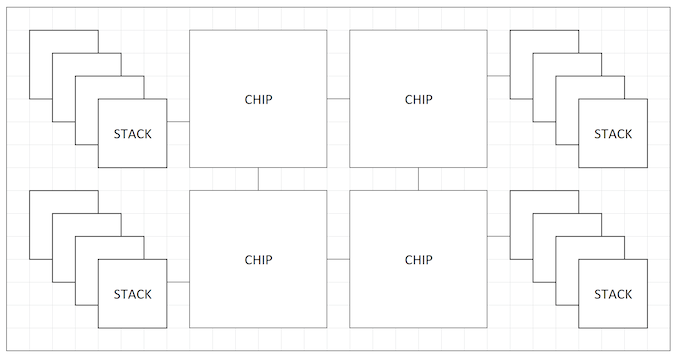

The nature of the Financial Analyst Day means that AMD didn’t go into too much detail here, aside from a few diagrams, but the company was clear that it sees its aggressive roadmap for chiplet and 3D integration to lead to this X3D design, where the X stands for ‘hybrid’. AMD’s diagrams show four main compute chiplets, arranged in a 2x2 pattern, and then 4-high stacked die with one per chiplet. All of these chips are then on a large interposer underneath.

Representation of AMD's diagram

In this case, it seems that the ‘die stacking’ element points to HBM or some form of memory, while the compute chiplets in the middle are only one high, but all connected through the interposer. AMD is claiming that this level of integration offers a 10x increase in bandwidth density, allowing more data to be shuttled from the memory stacks into the cores (and hopefully from storage into the memory stacks too).

The new packaging technology was listed as ‘future’, with no confirmed date. With AMD today announcing its new CDNA architecture for programmable compute graphics solutions, that sort of product would fit in really well here. With AMD’s prowess in CPU chiplet design, there could also be additional scope in future enterprise CPU developments as well. Graphics is a bit more farfetched, as the chiplet paradigm in graphics is a tricky one to solve.

We asked AMD more information about it, as to whether it correlates to any of TSMC’s latest packaging developments such as CoWoS or LIPINCON, however AMD stated that more would be detailed closer to the time at a dedicated event. We requested an AMD Architecture Day as soon as travel will allow. More to come as we find out about it.

Interested in more of our AMD Financial Analyst Day 2020 Coverage? Click here.

12 Comments

View All Comments

hakabakkjanu - Thursday, March 12, 2020 - link

Attend any major tech exhibition and you’ll find Intel announcing or reannouncing mildly improved processors. Whether you’re at IFA in Berlin, CES in Las Vegas, or Computex in Taipei, the spiel is always the same: the future is wireless, battery life matters to everyone, and there are a lot of people with five-year-old PCs who might notice a difference if they buy a new Intel-powered computer. It’s all painfully incremental and out of sync with Apple’s product cadence. Apple will give you, at most, two years with an iPhone before enticing you into upgrading, whereas Intel is trying to convince people with PCs that are half a decade old to do the same. https://rentacar.guru https://pakistani.guru https://realproperty.onlTomatotech - Saturday, August 15, 2020 - link

That's the best spam comment I've seen in a long while. You had me believing you were genuine .. right up to the spam at the end. Have a fake AnandTech Award.